深圳市浩德电子有限公司

- 浩德电子

- 产品展示

-

日光灯板

型号:日光灯板-006

材料:铝

厚度:0.6---3.0

日光灯板

型号:日光灯板-006

材料:铝

厚度:0.6---3.0

-

COB集成灯珠板

型号:COB集成灯珠板-005

材料:铝

厚度:0.6---3.0

COB集成灯珠板

型号:COB集成灯珠板-005

材料:铝

厚度:0.6---3.0

-

LED电视背光系列

型号:LED电视背光系列03

材料:铝

厚度:0.6---3.0

LED电视背光系列

型号:LED电视背光系列03

材料:铝

厚度:0.6---3.0

-

LED电视背光系列

型号:LED电视背光系列02

材料:铝

厚度:0.6---3.0

LED电视背光系列

型号:LED电视背光系列02

材料:铝

厚度:0.6---3.0

-

LED电视背光系列

型号:LED电视背光系列01

材料:铝

厚度:0.6---3.0

LED电视背光系列

型号:LED电视背光系列01

材料:铝

厚度:0.6---3.0

-

柔性线路板

型号:柔性线路板-005

材料:聚酰亚胺或聚酯薄膜

厚度:

柔性线路板

型号:柔性线路板-005

材料:聚酰亚胺或聚酯薄膜

厚度:

-

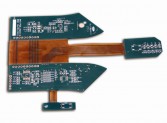

柔性线路板

型号:柔性线路板-004

材料:聚酰亚胺或聚酯薄膜

厚度:

柔性线路板

型号:柔性线路板-004

材料:聚酰亚胺或聚酯薄膜

厚度:

-

柔性线路板

型号:柔性线路板-003

材料:聚酰亚胺或聚酯薄膜

厚度:

柔性线路板

型号:柔性线路板-003

材料:聚酰亚胺或聚酯薄膜

厚度:

-

柔性线路板

型号:柔性线路板-002

材料:聚酰亚胺或聚酯薄膜

厚度:

柔性线路板

型号:柔性线路板-002

材料:聚酰亚胺或聚酯薄膜

厚度:

-

柔性线路板

型号:柔性线路板-001

材料:聚酰亚胺或聚酯薄膜

厚度:

柔性线路板

型号:柔性线路板-001

材料:聚酰亚胺或聚酯薄膜

厚度:

-

- 服务支持

- 我们优势

- 联系我们